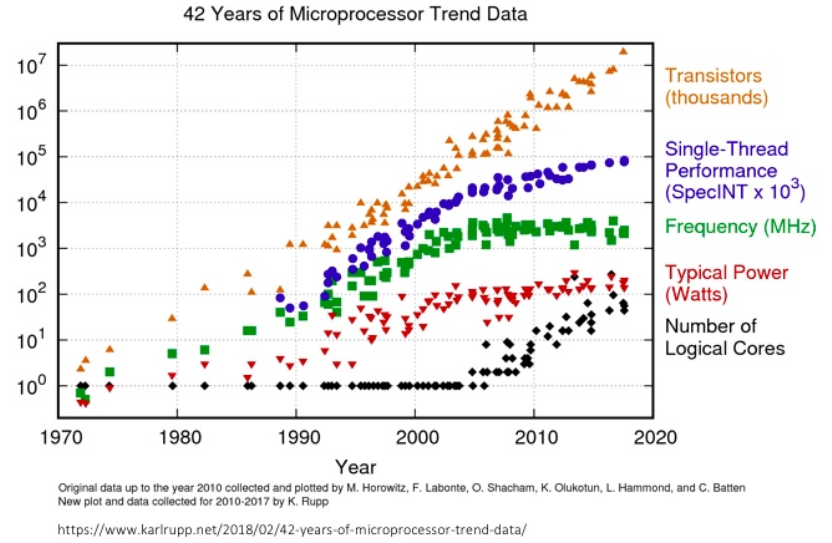

Standford 在今年8月發表了一篇標題為 “Spatial: A Language and Compiler for Application Accelerators” 的論文, 在談論之前必須從 Moore’s Law 的結束談起, 在 CPU 的過程中數年前即開始陷入瓶頸, 儘管製程不斷精進, 然而單核效能增長放緩, 於是人們只能在處理器中放入更多的核心:

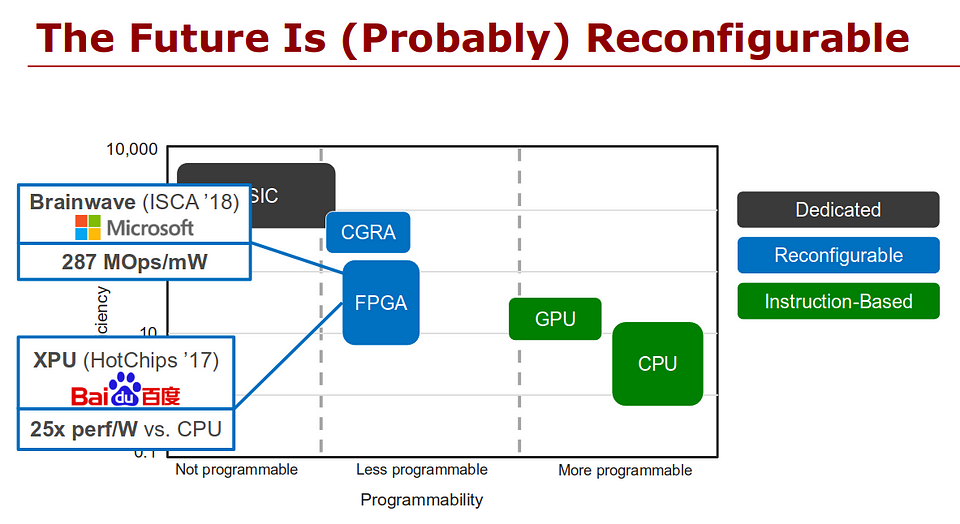

CPU 有著相當多的優點, 其中最重要者即是 Programmability. 然而缺點即在於 Power Efficiency. 而近年不斷提升效能與程式彈性的 GPU 儘管是部份問題的方案, 然而對於非俱備 data/task parallelism 的應用依然有著其侷限性. 在如此的情況下, 對於高度計算量的需求變開始著眼於其他計算裝置. 現今而言 FPGA, CGRA 等 Reconfigurable Device 提供了另一選擇.

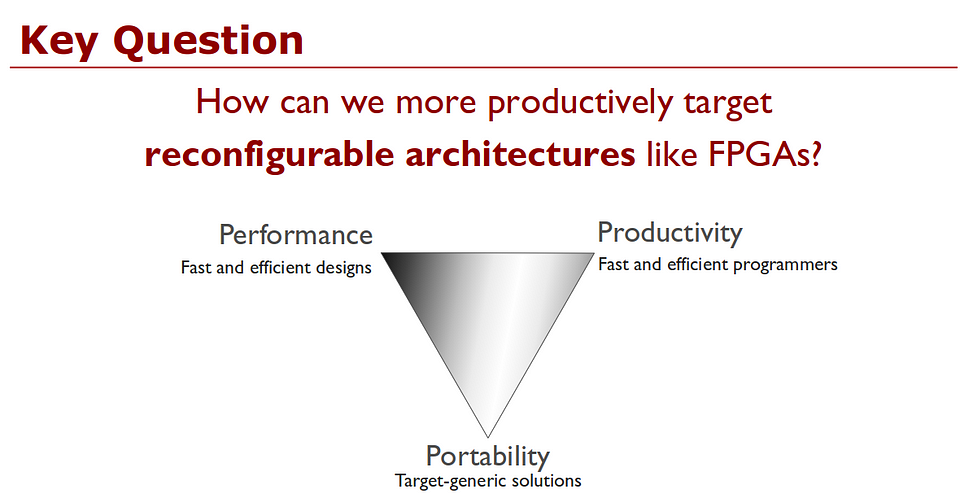

而這類裝置的特性缺點即在於對於 Programmability 上缺乏的彈性. 對於應用上而言, 依照以往的分工透過 Digital Logic Designer 與 Software Engineer 的協同工作的模式已經不足以應付多元且變化快速的各類應用. 因此為了加速而衍生了 High Level Synthesis (HLS) 的 Programming Model, 然而使用 HLS 特定平台撰寫的硬體設計有著移植性差且因為 framework 與 language 設計上效能侷限問題. 若涵蓋諸多相似但迥異的平台關鍵的問題在於 “如何能更有生產力地對類似 FPGA 的 reconfigurable 架構提供方案”, 而這帶來三個面向的考量:

- 性能(Performace) — 快速與有效的設計

- 生產力(Productivity) — 快速與有效的程式設計師

- 可移植性(Portability) — 通用性的方案

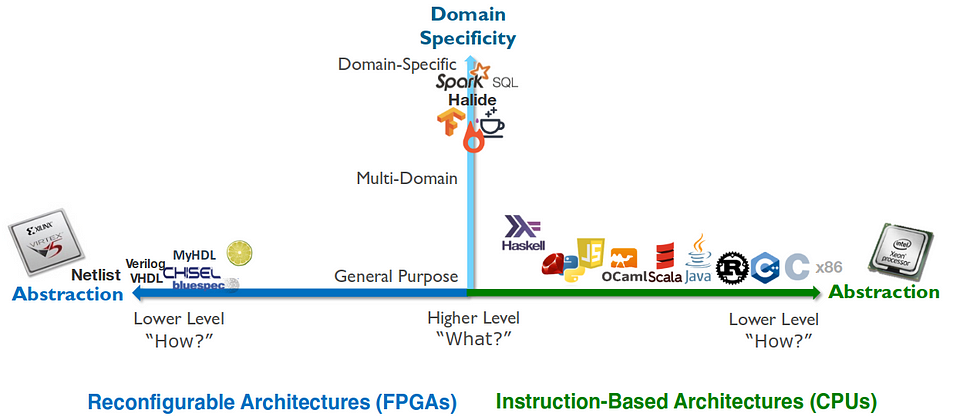

從程式語言的發展上, 可以觀察到近年在 CPU/GPU 等俱備 Programmablility 平台上, 針對解決特定面向範圍的問題提出了許多語言, 語言特性上逐漸往 Domain Specific 靠攏. 這裡列舉了自最靠近 CPU 的組語, C/C++, 網路應用 JavaScript, 簡單且便於流程控制的 Python, 較高抽象與數理方式的 Functional Language — Haskell. 最後是針對應用所設計的語言, Deep Learning 的 TensorFlow, Image Processing 的 Halide …等等, 然而 Digital Design 在發展上並沒有非常快速地往高度抽象的 “Domain Specific” 推移.

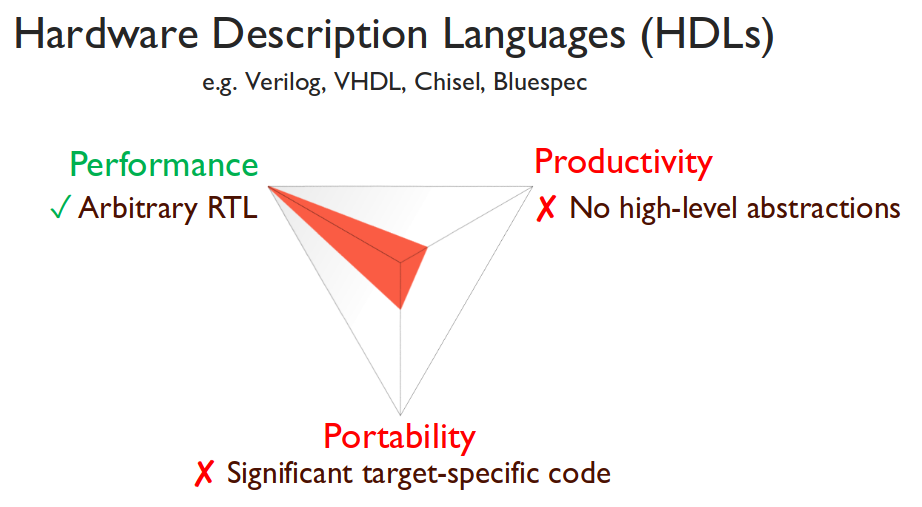

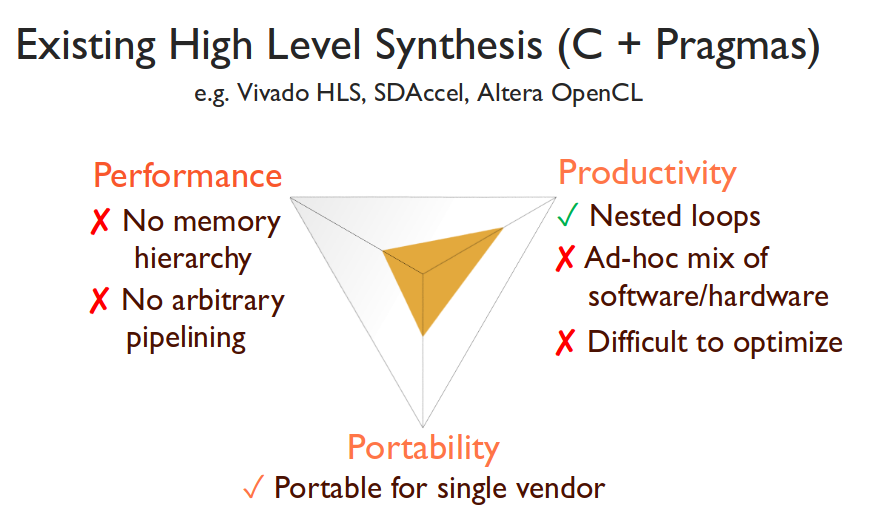

對於發展現況的了解後, 在切入 Spatial Language 定位前必須先了解目前主流的兩種 Programming Model (HDLs, HLS) 對於上面提出的三個面向的情況:

Spatial 的開發者認為現有 HDL 儘管有著最好的效能, 然而其生產力與可移植性是相當不佳的, 而 HLS 的方式儘管在 HDL 的兩個弱處有所改進, 然而依然存在著幾個比較大的問題:

- 缺乏 memory hierarchy 的架構考量

- 無法輕易地 pipelining

- 無法混合軟硬體設計

- 難以優化

- 單一平台

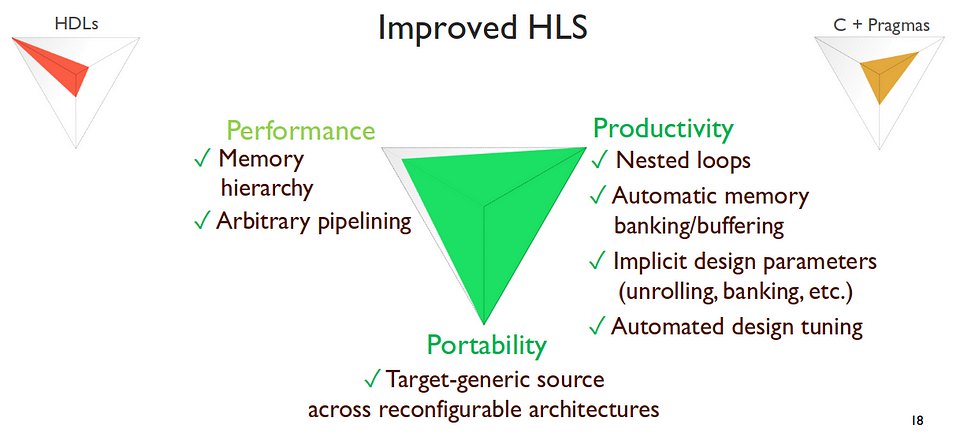

而 Spatial Language/Compiler 的提出最大的貢獻即在於相較以往的 HLS 方法提供了解決方案:

在類別上 Spatial 依然是屬於 HLS, 然而透過其設計與 compiler 分析與自動化, 提供了更為高效率的設計輸出, 語言設計上更為簡潔, 提供了撰寫難度降低的 programming model, 並且提供了多樣化的目標平台.

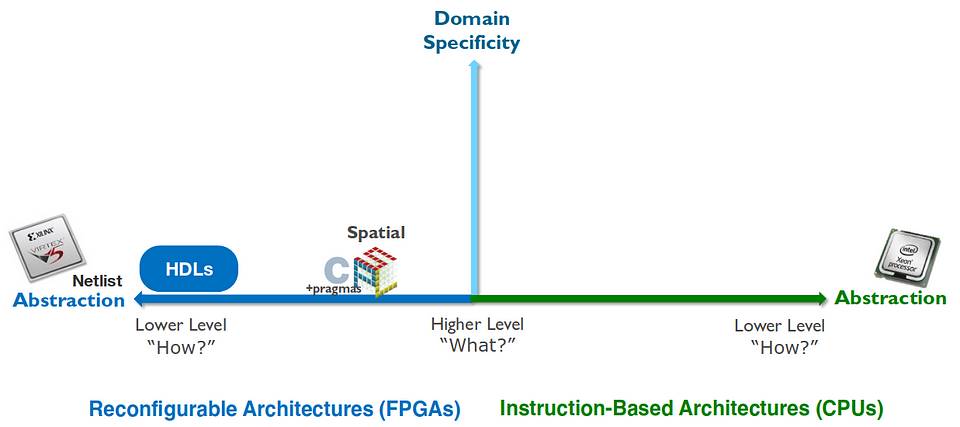

Spatial 設計者認為 HLS 與 Spatial 在抽象程度上定位如下圖:

Spatial 的優勢在於其獨特針對硬體設計抽象化的語言設計. 首先記憶體特性上提供了六種儲存類型:

- DRAM

- SRAM

- FIFO

- LineBuffer

- Reg

- RegFile

程式上提供了六類的控制/排程/介面/參數的語法:

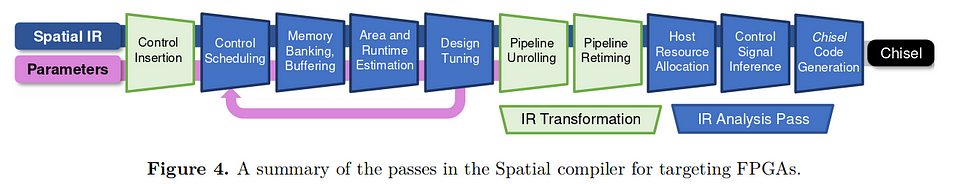

Spatial 即透過 memory 的類別使用與上述的語法等等設計組合, 在 Spatial Compiler 的內部會建構以 dataflow graph (DFG) 表示的 IR, 並針對這些語言特性所形成的 design space, 透過諸多的 compiler passes 中分析與尋找出較佳的設計, 並最終以 Chisel 的形式輸出.

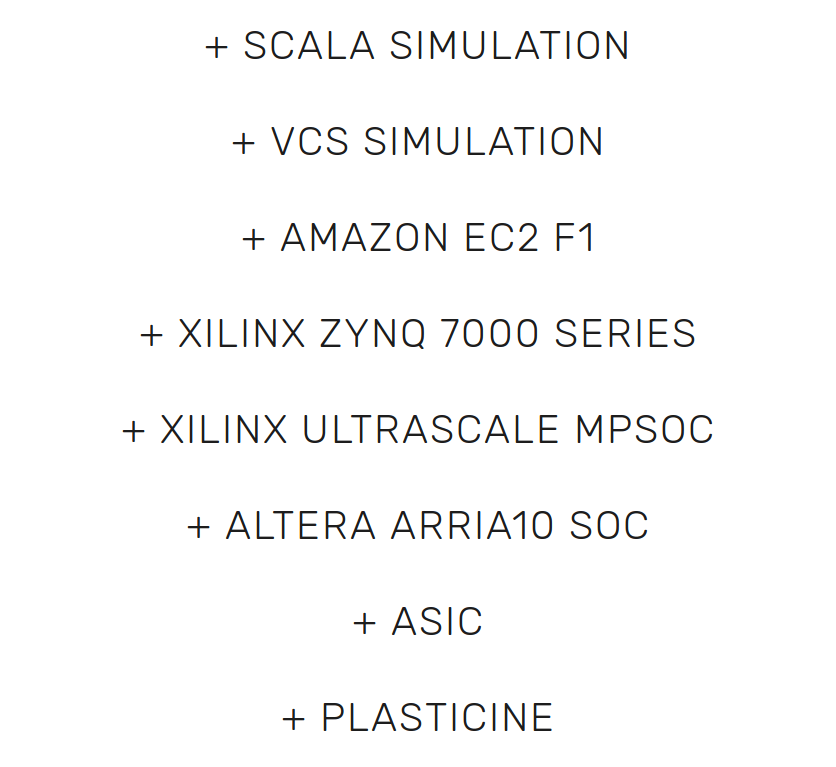

對於目標平台的支援程度上, Spatial 也並非隨便說說, 一開始推出即支援了多種平台, 涵蓋了模擬平台, FPGA 甚至搭配 Synopsys 的工具能夠有機會製作 ASIC, 官網上列出的平台如下:

近日也提供了簡短的說明文件, 以 Arria10 為例, 講述如何實作一個 Spatial backend. 後續會嘗試翻譯官方的教程. 一方面自學, 一方面拋磚引玉吸引更多開發者投入.

相關資源

沒有留言:

張貼留言